Product Summary

The EP20K100BC356-1 programmable logic device (PLD) family provide a low-cost alternative to high-volume gate array designs. The EP20K100BC356-1 is based on the OptiFLEX architecture, which minimizes die size while maintaining high performance and routability. The EP20K100BC356-1 is reprogrammable, and the EP20K100BC356-1 is 100% tested prior to shipment.

Parametrics

EP20K100BC356-1 absolute maximum ratings: (1)Supply voltage With respect to ground, VCC: -2.0 to 7.0V; (2)DC input voltage, VI: -2.0 to 7.0V; (3)DC output current, per pin, IOUT: -25 to 25mA; (4)Storage temperature No bias, TSTG: -65 to 150℃; (5)Ambient temperature Under bias, TAMB: -65 to 135℃; (6)Junction temperature PQFP, TQFP, and BGA packages, TJ: 135℃.

Features

EP20K100BC356-1 features: (1)Register-rich, look-up table (LUT-) based architecture; (2)OptiFLEX architecture that increases device area efficiency; (3)Typical gates ranging from 5,000 to 24,000 gates; (4)Built-in low-skew clock distribution tree; (5)100% functional testing of all devices; (6)test vectors or scan chains are not required.

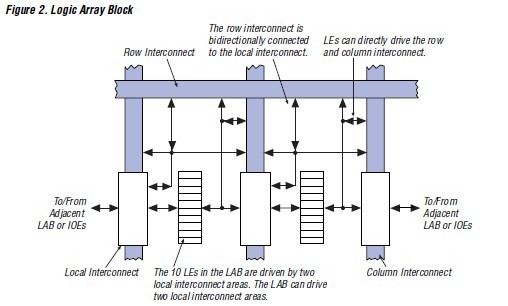

Diagrams

(China (Mainland))

(China (Mainland))