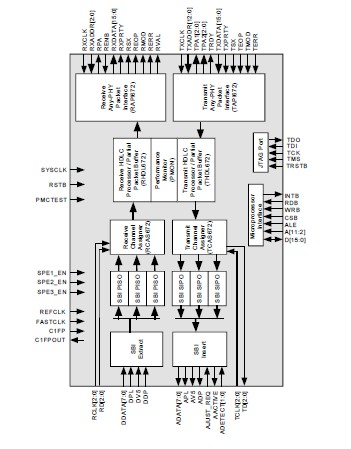

Product Summary

The PM7385-BI FREEDM-84A672 is a Frame Engine and Datalink Manager device. The PM7385-BI is a monolithic integrated circuit that implements HDLC processing for a maximum of 672 bi-directional channels. Applications are (1)IETF PPP interfaces for routers; (2)Frame Relay interfaces for ATM or Frame Relay switches and multiplexors; (3)FUNI or Frame Relay service inter-working interfaces for ATM switches and multiplexors; (4)Internet/Intranet access equipment; (5)Packet-based DSLAM equipment; (6)Packet over SONET; (7)PPP over SONET.

Parametrics

PM7385-BI absolute maximum ratings: (1)Case Temperature under Bias: -40°C to +85°C; (2)Storage Temperature: -40°C to +125°C; (3)Supply Voltage: (+3.3 Volt VDD3.3)-0.3V to +4.6V; (4)Supply Voltage: (+2.5 Volt VDD2.5)-0.3V to +3.5V; (5)Volatge on Any Pin: -0.3V to VDD3.3 + 0.3V; (6)Static Discharge Voltage: ±1000 V; (7)Latch-Up Current: ±100 mA; (8)DC Input Current: ±20 mA; (9)Lead Temperature: +230°C; (10)Absolute Maximum Junction Temperature: +150°C.

Features

PM7385-BI features: (1)Supports up to 672 bi-directional HDLC channels assigned to a maximum of 84 channelised or unchannelised links conveyed via a Scaleable Bandwidth Interconnect (SBI)interface; (2)Data on the SBI interface is divided into 3 Synchronous Payload Envelopes (SPEs). Each SPE can be configured independently to carry data for either 28 T1/J1 links, 21 E1 links, or 1 unchannelised DS-3 link; (3)Links in an SPE can be configured individually to operate in clear channel mode, in which case, all framing bit locations are assumed to be carrying HDLC data; (4)Links in an SPE can be configured individually to operate in channelised mode, in which case, the number of time-slots assigned to an HDLC channel is programmable from 1 to 24 (for T1/J1 links)and from 1 to 31 (for E1 links); (5)Supports three bi-directional HDLC channels each assigned to an unchannelised link with arbitrary rate link of up to 51.84 MHz when SYSCLK is running at 45 MHz. Each link may be configured individually to replace one of the SPEs conveyed on the SBI interface; (6)For each channel, the HDLC receiver supports programmable flag sequence detection, bit de-stuffing and frame check sequence validation. The receiver supports the validation of both CRC-CCITT and CRC-32 frame check sequences; (7)For each channel, the receiver checks for packet abort sequences, octet aligned packet length and for minimum and maximum packet length. The receiver supports filtering of packets that are larger than a user specified maximum value.

Diagrams

(China (Mainland))

(China (Mainland))