Product Summary

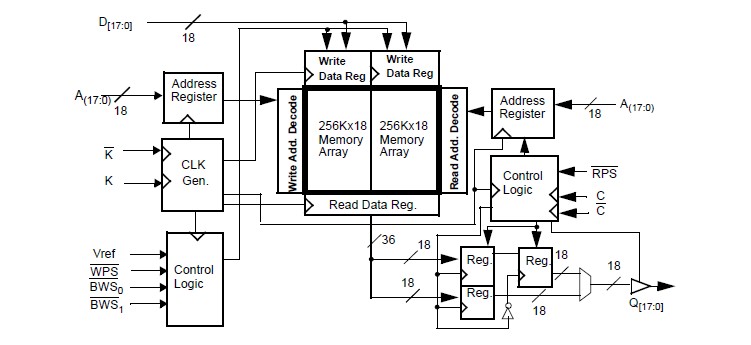

The CY7C1302DV25-167BZXC is a 2.5V Synchronous Pipelined SRAM equipped with QDR architecture. QDR architecture consists of two separate ports to access the memory array. The CY7C1302DV25-167BZXC has dedicated data outputs to support Read operations and the Write Port has dedicated data inputs to support Write operations. Access to each port is accomplished through a common address bus. The Read address is latched on the rising edge of the K clock and the Write address is latched on the rising edge of K clock. Depth expansion is accomplished with a Port Select input for each port. The CY7C1302DV25-167BZXC allows each port to operate independently. All synchronous inputs pass through input registers controlled by the K or K input clocks. All data outputs pass through output registers controlled by the C or C (or K or K in a single clock domain) input clocks. Writes are conducted with on-chip synchronous self-timed write circuitry.

Parametrics

CY7C1302DV25-167BZXC absolute maximum ratings: (1)Storage Temperature : –65°C to +150°C; (2)Ambient Temperature with Power Applied : –55°C to +125°C; (3)Supply Voltage on VCC Relative to GND[2]: –0.5V to +4.6V; (4)DC Voltage Applied to Outputs in High-Z State[2] : –0.5V to VCC + 0.5V, DC Input Voltage[2] : –0.5V to VCC + 0.5V; (5)Current into Outputs (LOW): 20 mA; (6)Static Discharge Voltage: >2001V (per MIL-STD-883, Method 3015); (7)Latch-up Current: >200 mA.

Features

CY7C1302DV25-167BZXC features: (1)Separate independent Read and Write data ports: Supports concurrent transactions; (2)167-MHz clock for high bandwidth: 2.5 ns Clock-to-Valid access time; (3)2-word burst on all accesses; (4)Double Data Rate (DDR)interfaces on both Read and Write ports (data transferred at 333 MHz)@ 167 MHz; (5)Two input clocks (K and K)for precise DDR timing: SRAM uses rising edges only; (6)Two input clocks for output data (C and C)to minimize clock-skew and flight-time mismatches; (7)Single multiplexed address input bus latches address inputs for both Read and Write ports; (8)Separate Port Selects for depth expansion; (9)Synchronous internally self-timed writes; (10)2.5V core power supply with HSTL Inputs and Outputs; (11)Available in 165-ball FBGA package (13 x 15 x 1.4 mm); (12)Variable drive HSTL output buffers; (13)Expanded HSTL output voltage (1.4V–1.9V); (14)JTAG Interface.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CY7C1302DV25-167BZXC |

Cypress Semiconductor |

SRAM 9MB (512Kbx18) 2.5V, 167MHz |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

CY7C006 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXCT |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AC |

|

IC SRAM 16KX8 DUAL 64LQFP |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))