Product Summary

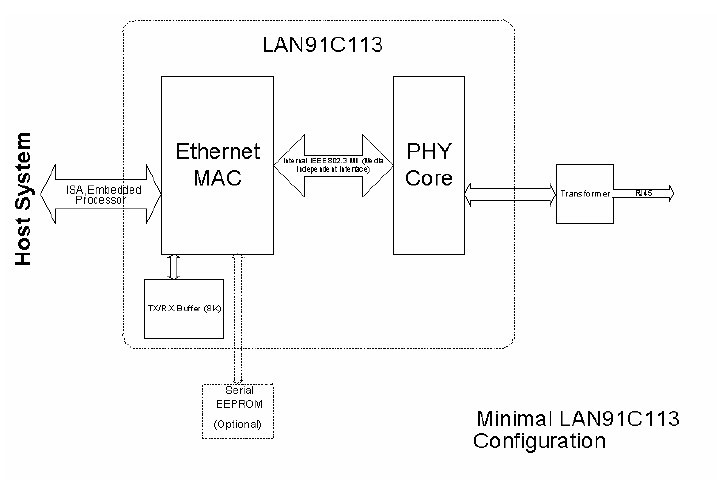

The SMSC LAN91C113-NC is a feast fast ethernet controller. For this third generation of products, flexibility and integration dominate the design requirements. The LAN91C113-NC is a mixed signal Analog/Digital device that implements the MAC and PHY portion of the CSMA/CD protocol at 10 and 100 Mbps. The design will also minimize data throughput constraints utilizing a 16-bit or 8-bit bus Host interface in embedded applications. The total internal memory FIFO buffer size is 8 Kbytes, which is the total chip storage for transmit and receive operations. The SMSC LAN91C113-NC is software compatible with the LAN9000 family of products. The LAN91C113-NC can automatically configure itself for 100 or 10 Mbps and Full or Half Duplex operation with the on-chip Auto-Negotiation algorithm. The LAN91C113-NC is ideal for media interfaces for embedded application desiring Ethernet connectivity as well as 100Base-TX/10Base-T adapter cards, motherboards, repeaters, switching hubs. The LAN91C113-NC operates from a single 3.3V supply. The inputs and outputs of the host Interface are 5V tolerant and will directly interface to other 5V devices.

Parametrics

LAN91C113-NC absolute maximum ratings: (1)Operating Temperature Range: 0℃ to 85℃; (2)Storage Temperature Range: -55℃ to + 150℃; (3)Lead Temperature Range (soldering, 10 seconds): +325℃; (4)Positive Voltage on any pin, with respect to Ground: VCC + 0.3V; (5)Negative Voltage on any pin, with respect to Ground: -0.3V; (6)Maximum VCC: +5V.

Features

LAN91C113-NC features: (1)Single Chip Ethernet Controller; (2)Dual Speed - 10/100 Mbps; (3)Fully Supports Full Duplex Switched Ethernet; (4)8 Kbytes Internal Memory for Receive and Transmit FIFO Buffers; (5)Enhanced Power Management Features; (6)Optional Configuration via Serial EEPROM Interface; (7)Supports 8, 16 Bit CPU Accesses; (8)Internal 16 Bit Wide Data Path (Into Packet Buffer Memory); (9)Early TX, Early RX Functions; (10)Built-in Transparent Arbitration for Slave Sequential Access Architecture; (11)Flat MMU Architecture with Symmetric Transmit and Receive Structures and Queues; (12)3.3V Operation with 5V Tolerant IO Buffers (See Pin List Description for Additional Details); (13)Single 25 MHz Reference Clock for Both PHY and MAC; (14)External 25Mhz-output pin for an external PHY supporting PHYs physical media.; (15)Low Power CMOS Design; (16)3.3V MII (Media Independent Interface) MACPHY Interface Running at Nibble Rate; (17)MII Management Serial Interface; (18)128 Pin QFP Package; Green, Lead-Free Package also available; (19)128 Pin TQFP Package, 1.0 mm height; Green, Lead-Free Package also available; (20)Temperature Range from 0℃ to 85℃.

Diagrams

(China (Mainland))

(China (Mainland))