Product Summary

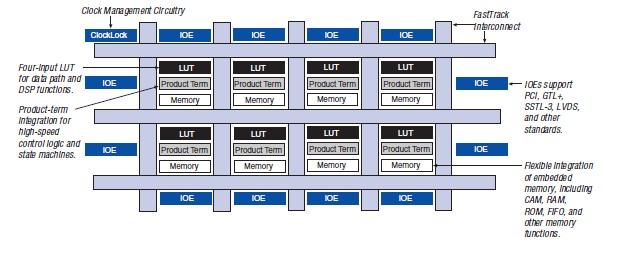

The EP20K1500EBC652-2X is a PLD designed with the MultiCore architecture, which combines the strengths of LUT-based and productterm- based devices with an enhanced memory structure. LUT-based logic provides optimized performance and efficiency for data-path, registerintensive, mathematical, or digital signal processing (DSP) designs. Product-term-based logic is optimized for complex combinatorial paths, such as complex state machines. The EP20K1500EBC652-2X is a superset of APEX 20K devices and include additional features such as advanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. In addition, the EP20K1500EBC652-2X extend the APEX 20K family to 1.5 million gates.

Parametrics

EP20K1500EBC652-2X absolute maximum ratings: (1)VCCINT Supply voltage With respect to ground: –0.5 to 3.6 V; (2)VCCIO: –0.5 to 4.6 V; (3)VI DC input voltage: –2.0 to 5.75 V; (4)IOUT DC output current, per pin: –25 to 25 mA; (5)TSTG Storage temperature No bias: –65 to 150 ° C; (6)TAMB Ambient temperature Under bias: –65 to 135 ° C; (7)TJ Junction temperature PQFP, RQFP, TQFP, and BGA packages, under bias: 135 ° C; (8)Ceramic PGA packages, under bias: 150 ° C.

Features

EP20K1500EBC652-2X features: (1)MultiCoreTM architecture integrating look-up table (LUT)logic, product-term logic, and embedded memory; (2)LUT logic used for register-intensive functions; (3)Embedded system block (ESB)used to implement memory functions, including first-in first-out (FIFO)buffers, dual-port RAM, and content-addressable memory (CAM); (4)ESB implementation of product-term logic used for; (5)combinatorial-intensive functions; (6)30,000 to 1.5 million typical gates (see Tables 1 and 2); (7)Up to 51,840 logic elements (LEs); (8)Up to 442,368 RAM bits that can be used without reducing available logic; (9)Up to 3,456 product-term-based macrocells.

Diagrams

(China (Mainland))

(China (Mainland))